2. 河海大学江苏省输配电装备技术重点实验室,常州,213022

2. Jiangsu Key Laboratory of Power Transmission and Distribution Equipment Technology, Hohai University, Changzhou, 213022, China

与Si基电力电子器件相比,SiC基电力电子器件具有更优良的器件特性,可望大幅提高电力电子变换器的性能。高开关频率是SiC器件应用研究的重要方向之一[1-2],随着开关频率的增大,寄生电感对器件动态开关过程的影响程度也越来越大,导致开关波形产生严重振荡,增大器件应力和电磁干扰(Electromagnetic interference,EMI),无法充分发挥SiC器件在高速开关下低开关损耗的性能优势[3-5]。

近些年,国内外诸多学者针对电路寄生电感对SiC器件开关特性的影响进行了研究,归纳其研究方法主要分为以下3种:(1) 将寄生电感当作一个感性网络,提取电路或功率模块的寄生电感,通过建模和仿真探究寄生电感的影响,但没有对各部分寄生电感的影响分别进行研究,没有明确各部分寄生电感对SiC器件开关特性的影响程度[6-7];(2) 对各部分寄生电感的影响进行理论分析,但开关器件的非线性和实际电路存在的寄生参数,导致模型阶数较高,为便于分析,通常都需要进行一些近似和假设,且其理论推导结果通常较为复杂,并不能直接从表达式中得出寄生电感的影响规律,缺少实验的验证,对实际电路设计的指导意义有限[8];(3) 采用实验方法,对各部分寄生电感对开关特性的影响进行了测试分析,但其设定的寄生电感值并未考虑实际布局的限制,得出的是各部分寄生电感大小影响的单一关系,所得结果仍不足以支撑SiC器件开关电路的合理布局[9-17]。

考虑到SiC器件建模的准确程度受电路寄生参数影响,理论分析较难得出逼近真实的研究结果,本文采用理论定性分析与实验定量研究相结合的方法,先建立了考虑寄生电感的SiC MOSFET基本开关电路的数学模型,确立了影响开关特性的主要因素,然后建立SiC器件高速开关电路双脉冲测试平台,对各部分寄生电感对SiC器件开关性能的影响进行系统研究。首先,基于电流回路的概念,将各部分寄生电感归为以下3类:主开关回路寄生电感LD,栅极回路寄生电感LG和共源极寄生电感LS。结合实际电路布局,考虑3种寄生电感的取值范围,从开关时间、振荡和尖峰等方面揭示寄生电感对SiC MOSFET开关特性的影响规律,量化其影响程度。在此基础之上,根据SiC高速开关电路实际布局的限制,在布局紧凑程度或回路走线总长度相对不变的情况下,对各部分寄生电感的匹配关系进行研究,对比不同寄生参数组合下SiC器件开关速度、开关能量和电压电流应力的变化,归纳得出SiC器件开关过程受寄生参数影响的特性规律,从而指导SiC基高速开关电路的布局设计。

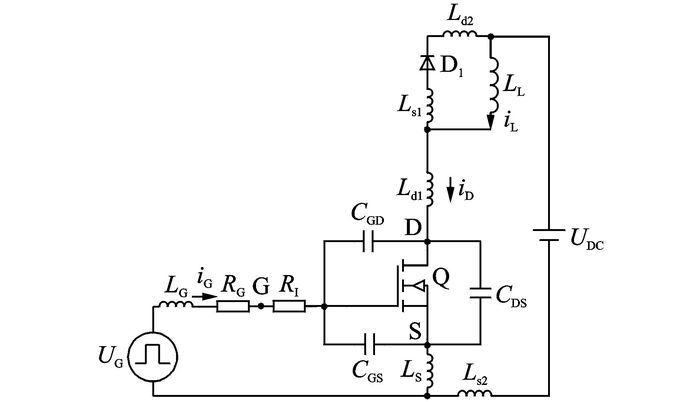

1 SiC MOSFET开关特性建模与分析考虑寄生电感的SiC MOSFET双脉冲测试电路原理图如图 1所示,Q为SiC MOSFET开关管,CGS,CGD和CDS分别为栅源极、栅漏极和漏源极间寄生电容,LG为栅极驱动电路到栅极引脚之间的寄生电感,LS为源极引脚到栅极驱动电路之间存在的寄生电感,主开关回路中存在的寄生电感包括MOSEET漏极引脚分布电感Ld1、二极管寄生电感Ls1、PCB走线寄生电感Ld2和Ls2,RI和RG分别为开关管内部栅极寄生电阻和外部驱动电阻,D1为续流二极管,LL为负载电感。为了合理简化电路,从闭合回路的角度出发,将双脉冲电路中的寄生电感分别归类到栅极回路和主开关回路[10],可以将主开关回路的电感简化,令漏极寄生电感LD=Ld1+Ld2+Ls1+Ls2,各部分寄生电感即归为以下3大类:主开关回路漏极寄生电感LD、栅极回路寄生电感LG和共源极寄生电感LS。

|

图 1 考虑各部分寄生电感的SiC MOSFET双脉冲电路原理图 Figure 1 Schematic of double-pulse circuit of SiC MOSFET considering each parasitic inductance |

栅极回路寄生电感LG引起的感应电压须满足[9]

| ${L_{\rm{G}}} \cdot \frac{{{\rm{d}}{i_{\rm{G}}}}}{{{\rm{d}}t}} < \Delta {U_{{\rm{G }}(\max )}}$ | (1) |

式中ΔUG(max)为栅极允许的最大电压振荡尖峰值,且由于栅极电压尖峰引起的漏极电流尖峰需满足

| ${g_{{\rm{fs}}}} \cdot \Delta {U_{{\rm{G }}(\max )}} < 10\% \cdot {I_{\rm{N}}}$ | (2) |

式中:gfs为SiC MOSFET的跨导;IN为额定电流。则栅极回路寄生电感LG须满足

| ${L_{\rm{G}}}\cdot\frac{{{\rm{d}}{i_{\rm{G}}}}}{{{\rm{d}}t}} < \frac{{10\% \cdot {I_{\rm{N}}}}}{{{g_{{\rm{fs}}}}}}$ | (3) |

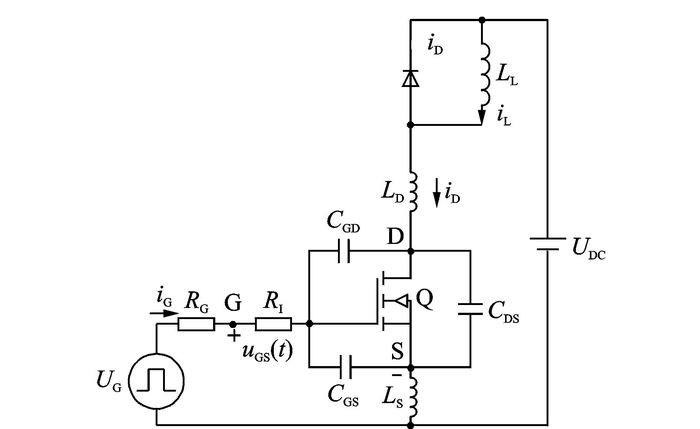

以定额为1 200 V/35 A的SiC MOSFET为例,gfs=3.7 S,当diG/dt=4 A/100 ns、额定电流IN=20 A时,LG<13 nH。所以在实际设计中,对减小栅极回路寄生电感的要求较高,主功率回路的额定电流越大,需要更大的峰值驱动电流和更高的diG/dt,因此栅极回路的寄生电感就必须更小。也即以驱动电路合理设计而言,必须保证很小的栅极回路寄生参数。在这种情况下,栅极回路寄生电感对功率电路的影响就会很小。因此,为便于分析推导建立数学模型降低阶数,这里暂且忽略栅极寄生电感LG,得到如图 2所示的简化等效电路。

|

图 2 双脉冲电路简化等效电路 Figure 2 Simplified equivalent chematic of double-pulse circuit |

由于SiC MOSFET在开关瞬间工作在饱和区,漏极电流满足

| ${i_{\rm{D}}}\left( t \right) = {g_{{\rm{fs}}}}({u_{{\rm{GS}}}}\left( t \right) - {U_{{\rm{TH}}}})$ | (4) |

式中:UTH为SiC MOSFET的阈值电压;gfs为跨导。由于开关瞬间的diD/dt作用于主功率回路的寄生电感LS和LD上产生感应电压,开关管两端承受的电压应力为输入电压UDC与此感应电压相叠加,表示为

| ${u_{{\rm{DS}}}}\left( t \right) = {U_{{\rm{DC}}}} - ({L_{\rm{D}}} + {L_{\rm{S}}}){\rm{ }}\frac{{{\rm{d}}{i_{\rm{D}}}\left( t \right)}}{{{\rm{d}}t}}$ | (5) |

开关回路方程同式(5),栅极回路方程为

| $\begin{array}{l} {U_{\rm{G}}} = {R_{\rm{G}}}({C_{{\rm{GS}}}}\frac{{{\rm{d}}{u_{{\rm{GS}}}}\left( t \right)}}{{{\rm{d}}t}} + {C_{{\rm{GD}}}}\frac{{{\rm{d}}{u_{{\rm{GD}}}}\left( {{\rm{ }}t} \right)}}{{{\rm{d}}t}}{\rm{ }}) + \\ \quad \quad \quad \quad {u_{{\rm{GS}}}}\left( t \right) + {L_{\rm{S}}}\frac{{{\rm{d}}{i_{\rm{D}}}\left( t \right)}}{{{\rm{d}}t}} \end{array}$ | (6) |

联立式(5,6) 得到栅源极电压uGS(t)的二阶微分方程为

| $\begin{align} & \quad {{U}_{\text{G}}}={{R}_{\text{G}}}{{C}_{\text{GD}}}{{g}_{\text{fs}}}({{L}_{\text{D}}}+{{L}_{\text{S}}})\text{ }\frac{\text{d}u_{\text{GS}}^{2}\left( t \right)}{\text{d}{{t}^{2}}}\text{ }+ \\ & \left[ {{R}_{\text{G}}}({{C}_{\text{GS}}}+{{C}_{\text{GD}}})+{{L}_{\text{S}}}{{g}_{\text{fs}}} \right]\frac{\text{d}{{u}_{~}}_{\text{GS}}\text{ }\left( t \right)}{\text{d}t}\text{ }+{{u}_{\text{GS}}}\left( t \right) \\ \end{align}$ | (7) |

利用Laplace变换,解微分方程得到uGS(t)的分段表达式为

| $\begin{array}{l} {u_{{\rm{GS}}}}\left( t \right) = \\ {U_{{\rm{GH}}\left( 1 \right)}} - {U_{{\rm{GH}}\left( 2 \right)}}{{\rm{e}}^{\left( { - t/{T_1}} \right)}}(\cos {\omega _1}t + \frac{{\sin {\omega _1}t}}{{{\omega _1}{T_1}}})\\ \quad \quad 4{y_1} \ge {y_2}^2 \end{array}$ | (8) |

| $\begin{array}{l} {U_{{\rm{GH}}\left( {\rm{1}} \right)}} - \frac{{{U_{{\rm{GH}}\left( {\rm{2}} \right)}}}}{{{T_2} - {T_3}}}\left[ {{T_2}{{\rm{e}}^{\left( { - t/{T_2}} \right)}} - {T_3}{{\rm{e}}^{\left( { - t/{T_3}} \right)}}} \right]\\ \quad \quad 4{y_1} < {y_2}^2 \end{array}$ | (9) |

式中:y1=RGCGDgfs(LD+LS);y2=RG(CGS+CGD)+LSgfs;时间常数

| ${u_{{\rm{GS}}}}\left( t \right) \approx {U_{{\rm{GH }}\left( {\rm{1}} \right){\rm{}}}} - {U_{{\rm{GH }}\left( {\rm{2}} \right){\rm{}}}}\cos \frac{1}{{\sqrt {{y_1}} }}t$ | (10) |

漏极电流变化率为

| $\frac{{{\rm{d}}{i_{\rm{D}}}\left( t \right)}}{{{\rm{d}}t}}{\rm{ }} \approx - \frac{{{g_{{\rm{fs}}}}{U_{{\rm{TH}}}} + {I_{\rm{L}}}}}{{{R_{\rm{G}}}{C_{{\rm{GD}}}}g{_{{\rm{fs}}}}({L_{\rm{D}}} + {L_{\rm{S}}})}}{\rm{ }}t$ | (11) |

关断电压振荡的超调量可以写成

| $\Delta {{U}_{\text{off}}}\approx \sqrt{\frac{2{{I}_{\text{L}}}~({{U}_{\text{TH}}}+{{I}_{\text{L}}}/{{g}_{~}}_{\text{fs}})}{{{R}_{\text{G}}}}}\text{ }\cdot \sqrt{\frac{({{L}_{\text{D}}}+{{L}_{\text{S}}})}{{{C}_{\text{GD}}}}}$ | (12) |

若4y1≪y22,则栅源极间电压的方程可以简化为

| ${u_{{\rm{GS}}}}\left( t \right) \approx {U_{{\rm{GH }}\left( {\rm{1}} \right){\rm{}}}} - {U_{{\rm{GH }}\left( {\rm{2}} \right){\rm{}}}}{{\rm{e}}^{\left( { - t/{y_2}} \right)}}$ | (13) |

关断电压振荡的超调量可以写成

| $\Delta {{U}_{\text{off}}}\approx ({{U}_{\text{TH}}}+{{I}_{\text{L}}}/{{g}_{\text{fs}}})\cdot \frac{{{g}_{\text{fs}}}({{L}_{\text{D}}}+{{L}_{\text{S}}})}{{{R}_{\text{G}}}{{C}_{~}}_{\text{GD}}+{{g}_{\text{fs}}}{{L}_{\text{S}}}~}$ | (14) |

由以上推导可知,开关特性主要受到漏极和源极寄生感的影响,随着寄生电感(LD+LS)的增大,漏极电流变化率减小,关断电压尖峰增大。在4y1≪y22的极端情况下,随着源极寄生电感LS的增大,gfsLS的影响占主导地位,关断电压尖峰减小,继续增大LS,gfsLS的主导作用降低,关断电压尖峰几乎不变。

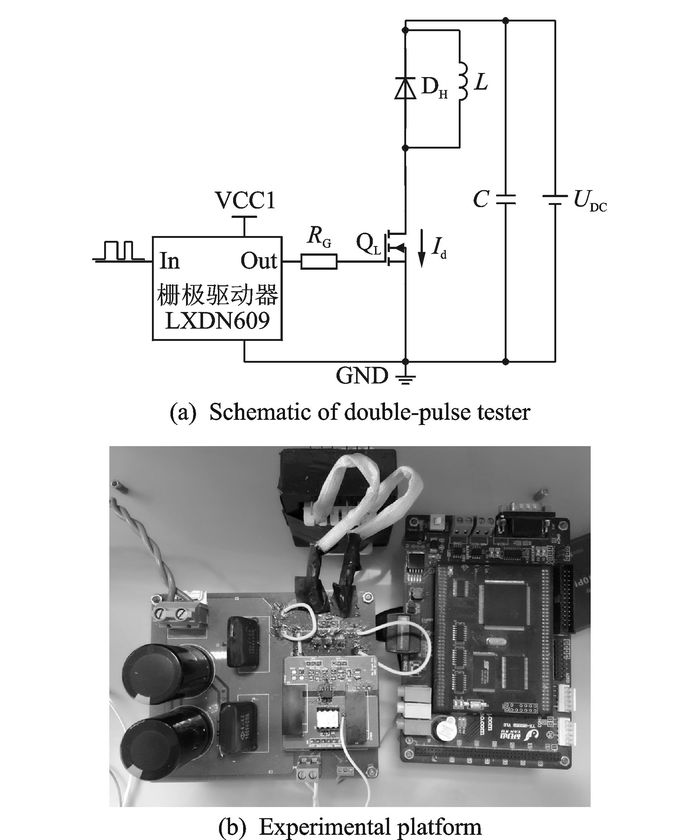

2 各部分寄生电感对开关特性的影响为了量化分析各部分寄生电感对SiC MOSFET开关过程的影响,制作了双脉冲电路测试平台,图 3(a,b)所示分别为其原理图和实物照片。待测SiC MOSFET采用ROHM公司的SCH2080KE,其定额为1 200 V/35 A,续流二极管DH采用型号为SCS210KG的SiC肖特基势垒二极管(SBD)以减小反向恢复电流的影响,抑制由二极管引起的漏极电流尖峰。SiC MOSFET开通时,电感的等效并联电容和二极管的结电容产生的充电电流会导致漏极电流产生尖峰,影响测试结果准确性,因此电感采用单匝绕组以减小等效并联电容。功率器件的电压和电流波形通过Tektronix公司的高压差分探头(P5201)、高频电流探头(TCP2020) 测得。实验测试条件为:UDC=600 V,电感L=180 μH,SiC MOSFET驱动电路的正压设定为18 V,负压设定为-2.6 V。两个脉冲总时间Δtp为5 μs,输入直流电压为600 V时的电感电流最大值ILmax为17 A。

|

图 3 双脉冲测试电路原理图和样机照片 Figure 3 Schematic of double-pulse tester and experimental platform |

2.1 栅极寄生电感LG的影响

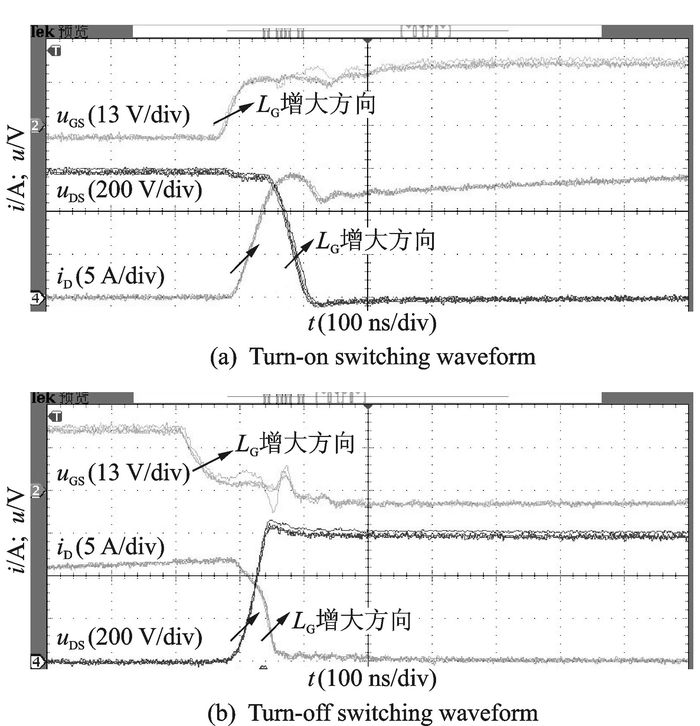

为便于分析电路走线引入的寄生电感对开关特性的影响,制作了小电感来模拟走线寄生电感,4种小电感的测试值分别为25,50,79和95 nH。在栅极引脚与驱动电路之间接入这些小电感模拟栅极寄生电感,图 4给出不同栅极寄生电感LG下,栅源极电压uGS、漏源极电压uDS和漏极电流iD的波形。由于栅极寄生电感LG会与SiC MOSFET的输入电容CISS(=CGS+CGD)谐振(阻尼系数为

|

图 4 不同LG下的uGS,uDS和iD开关波形 Figure 4 Switching waveforms of uGS, uDS and iD under different LG |

2.2 漏极寄生电感LD的影响

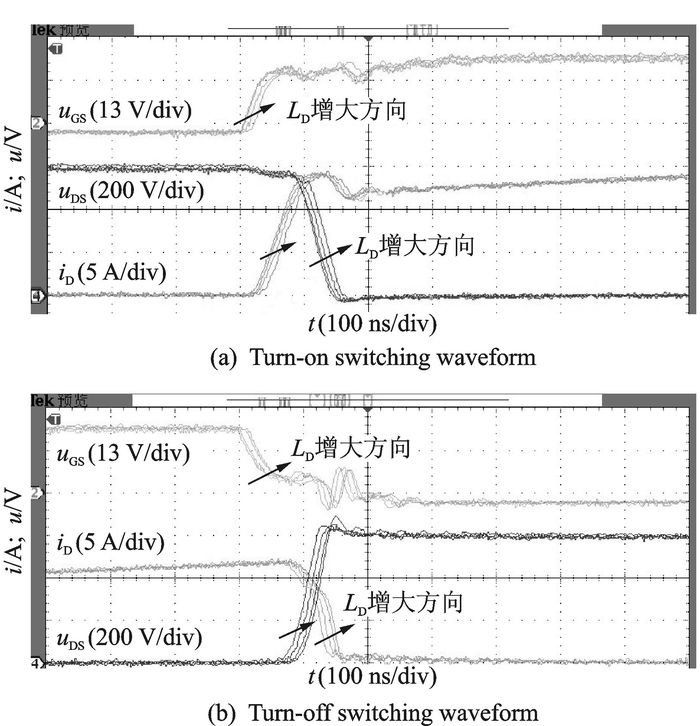

在高速开关状态下,漏极电流变化率diD/dt很大,在漏极寄生电感上引起感应电动势,开通时感应电动势的方向与母线电压方向相反,使得漏源极电压降低了ULD=LD·diD/dt。而关断瞬态感应电动势的方向与母线电压相同,叠加在开关管漏源极电压上产生漏极电压尖峰;另外,在开关瞬态,主开关回路寄生电感LD与SiC MOSFET的输出电容COSS(=CGD+CDS)和二极管的结电容、电感的寄生电容谐振,且该振荡会通过SiC MOSFET的密勒电容与栅极回路相耦合,从而使uDS,uGS和iD开关波形均产生振荡。在漏极接入感值分别为25,50,79和95 nH的小电感模拟漏极寄生电感,图 5给出不同LD下,栅源极电压uGS、漏源极电压uDS和漏极电流iD的开关波形。在开通过程中,随着漏极电感LD的增加,漏极电流iD的振荡幅度加大,而uDS受其影响不大;在关断过程中,随着LD的增加,iD和uDS的振荡都加剧,关断能量也加大。

|

图 5 不同LD下的uGS,uDS和iD开关波形 Figure 5 Switching waveforms of uGS, uDS and iD under different LD |

2.3 源极寄生电感LS的影响

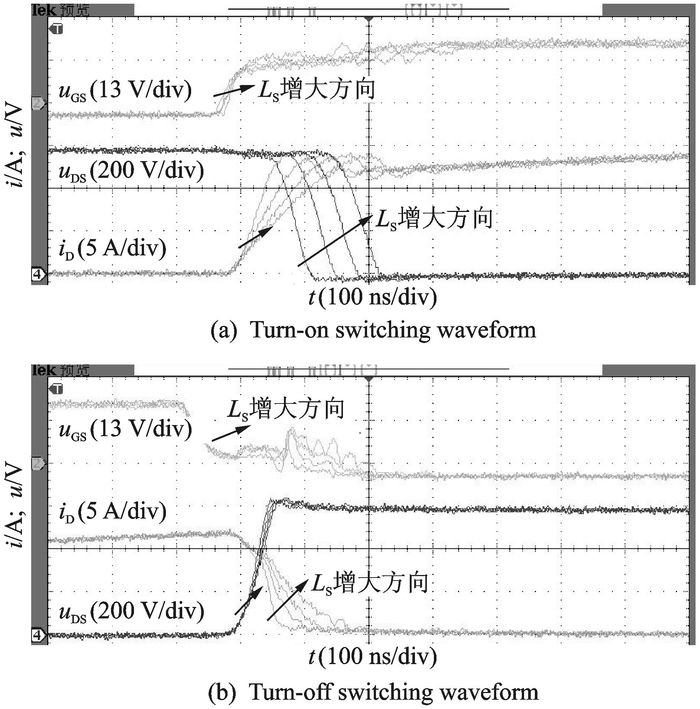

高速开关状态下,源极的电流变化率diD/dt在源极寄生电感LS上引起的感应电动势与驱动电压方向相反,使得开通和关断的驱动电压幅值均降低,减缓了开关过程,在主回路和驱动回路之间起“负反馈”的作用。在源极接入感值分别为25,50,79和95 nH的小电感时,图 6给出不同LS下,SiC MOSFET栅源极电压uGS、漏源极电压uDS和漏极电流iD的波形。由图可见,LS对SiC MOSFET开关波形延时影响比较明显。开通、关断瞬间,SiC MOSFET的开关时间均随着LS的增大而延长,电流变化率显著降低,开通电流尖峰和关断电压尖峰随着LS的增大均减小,但LS对漏源极电压变化率几乎没有影响。

|

图 6 不同LS下的uGS,uDS和iD开关波形 Figure 6 Switching waveforms of uGS, uDS and iD under different LS |

2.4 各部分寄生电感影响的量化分析 2.4.1 对开关期间电压、电流超调量的影响

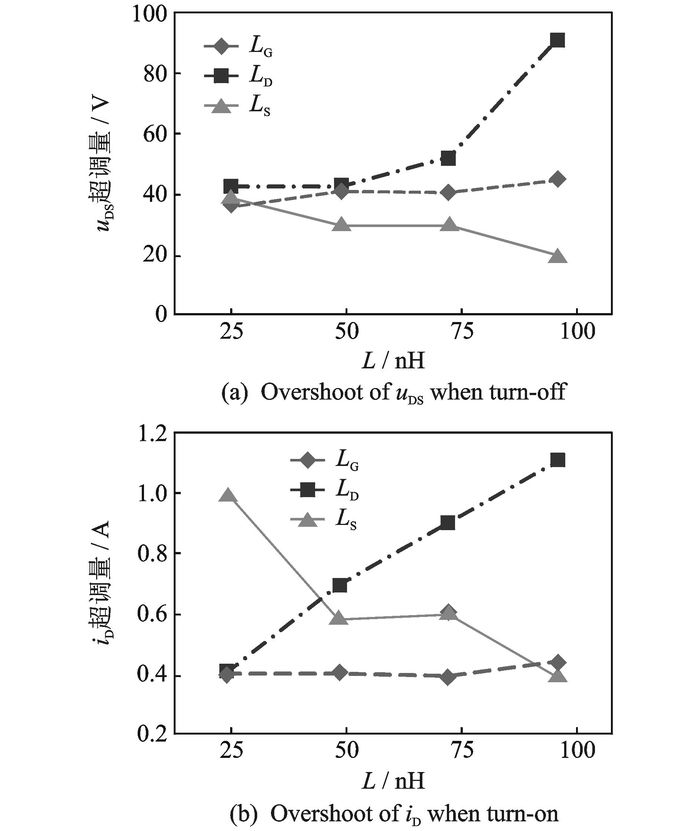

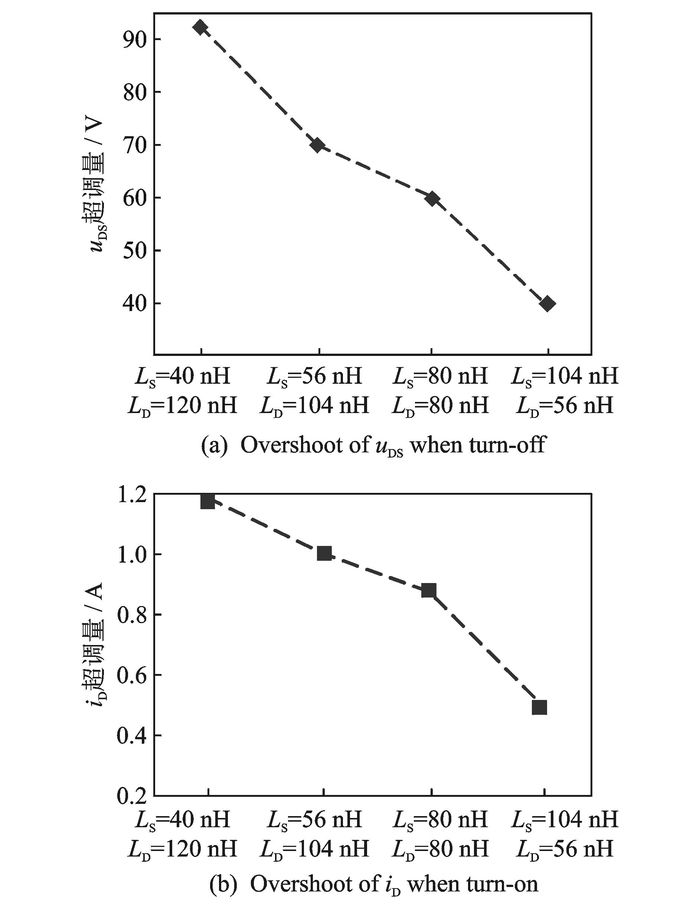

为了比较各部分寄生电感对开关特性的影响程度,图 7给出开关期间电压、电流超调量与寄生电感的关系曲线。与前述分析一致,改变栅极回路寄生电感LG对SiC MOSFET开关波形影响很小,随着LG的增大,uDS和iD的超调量几乎不变。主开关回路寄生电感LD和LS对uDS和iD的超调量均有较大的影响,LD越大,uDS和iD的超调量越大。与之相反,uDS和iD的超调量随着LS的增大而减小,即LS在驱动回路所起的负反馈作用对LD引起的开关波形振荡有一定抑制作用。

|

图 7 超调量与寄生电感的关系曲线 Figure 7 Relationship curves of voltage and current overshoot versus parasitic inductance |

2.4.2 开关时间

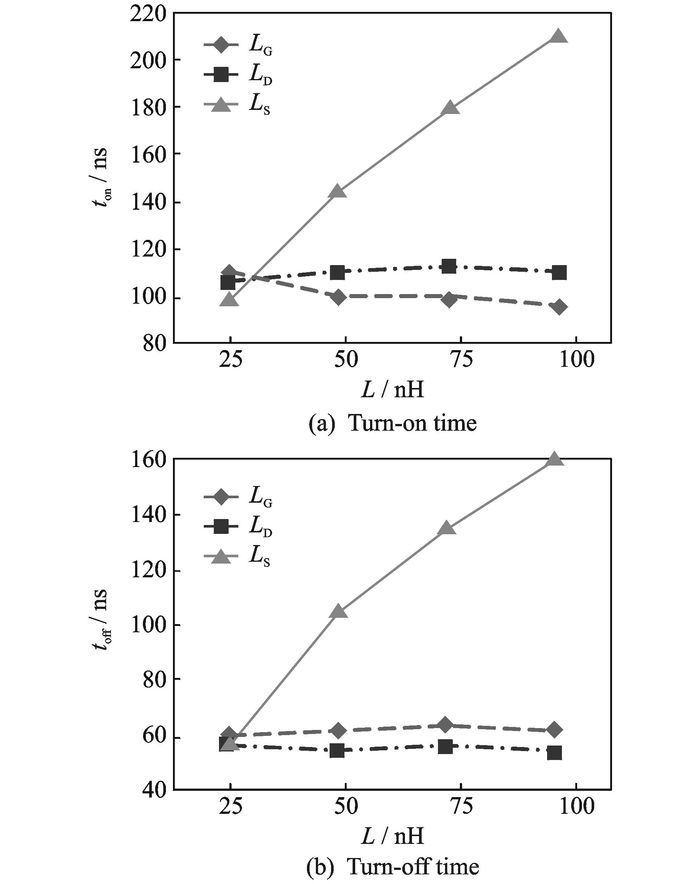

图 8为寄生电感LG, LD, LS对SiC MOSFET开通时间ton、关断时间toff的影响。由图可知,LG和LD对开通、关断时间的影响不是很明显,而寄生电感LS对SiC MOSFET的开关时间影响很大,随着LS的增大,开通、关断时间明显变长。

|

图 8 开关时间与寄生电感关系曲线 Figure 8 Relationship curves of turn-on and turn-off time versus parasitic inductance |

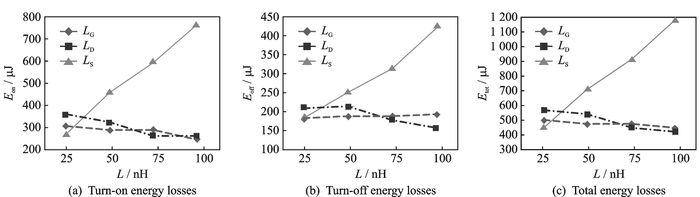

2.4.3 对开通和关断能量的影响

图 9给出了开关能量与寄生电感的关系曲线。随着LG的增大,开通和关断能量几乎不变。随着LD的增大,开通和关断能量略有减小,总开关能量减小幅度相对较小。由于LS的负反馈作用,LS对开关能量有很大的影响。当LS为95 nH时,总开关能量是相同感值的LD作用下总开关能量的3倍左右。

|

图 9 开关能量损耗与寄生电感关系曲线 Figure 9 Relationship curves of turn-on and turn-off energy losses versus parasitic inductance |

由以上分析比较可知,在高速开关情况下,栅极电感LG对栅极回路的振荡影响较大,但对主开关回路的影响较小;漏极电感LD对开通电流尖峰和关断电压尖峰的影响最大,对波形的振荡也有些影响;源极电感LS在主开关回路和栅极回路之间构成“负反馈”效应,对LD引起的波形振荡和电压尖峰有抑制作用,且减缓了漏极电流的变化速度,对开关速度和开通、关断能量的影响最为显著。

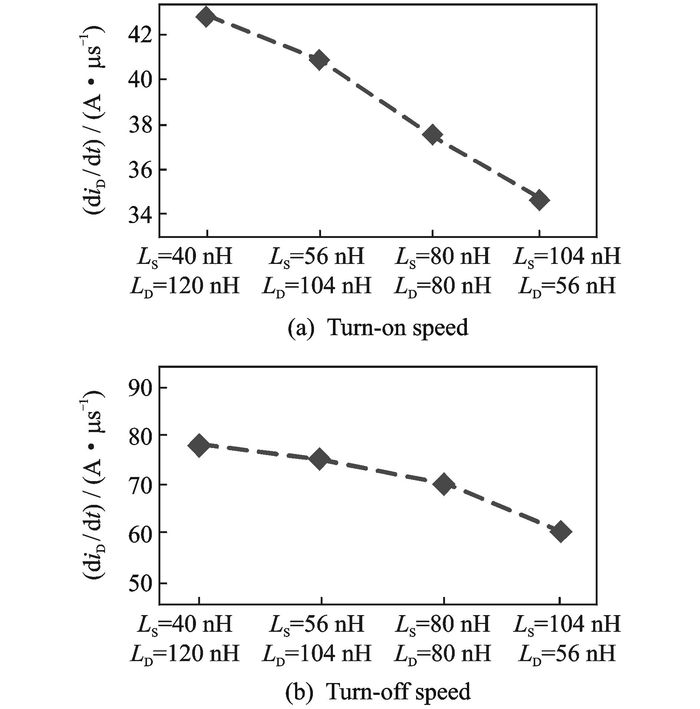

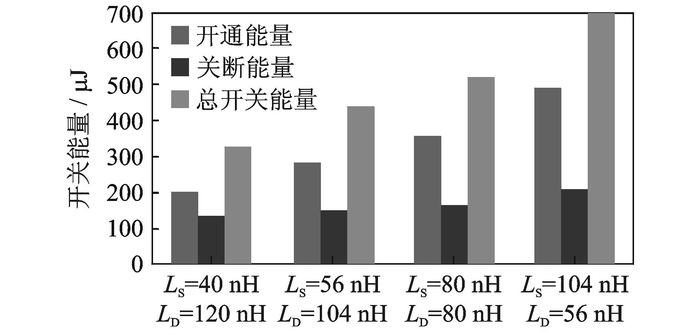

3 寄生电感综合匹配设计方法在高速开关驱动电路中,要求驱动回路与主功率回路的布局都比较紧凑,但PCB走线受实际布局限制,难以同时兼顾各部分寄生电感的减小。因驱动回路紧凑布局的优先级较高,一般要首先满足,因此在布局紧凑程度如回路走线总长不变的情况下,需权衡考虑源极LS与漏极LD的匹配,使得开关电路的特性在满足系统要求的情况下尽可能优化。实验中,在保持LD与LS的和基本不变的情况下,选取4组不同组合的LD与LS(见表 1),对漏极电压尖峰、漏极电流尖峰、开关管开关能量、开通关断速率di/dt和uGS振荡情况进行了测试对比。

| 表 1 不同组合的LD与LS Table 1 Different combinations of LD and LS |

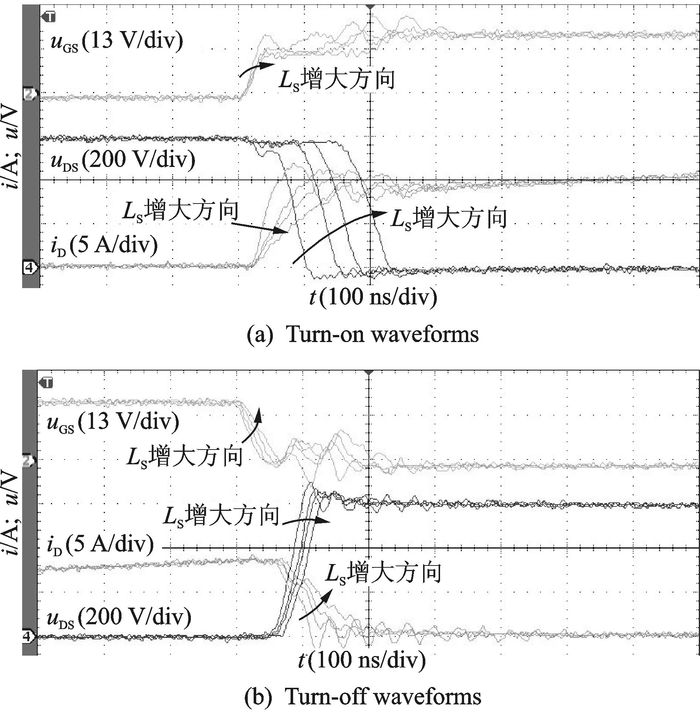

图 10给出不同LD与LS组合条件下开关管的开通和关断波形。LD与LS的总和基本不变的情况下,开关瞬间diD/dt随LS变化的曲线如图 11所示。在开通过程中,随着LS的增加,uGS的上升速度变慢,漏极电流iD的上升速度和漏极电压uDS的下降速度减缓,开通速度变慢,通过漏极电流iD和漏极电压uDS的乘积积分计算开关能量损耗,图 12给出了计算结果,开通损耗随LS的增大而增大,开通瞬态电流尖峰随LS的增大而减小。

|

图 10 开关管开关瞬间uGS, iD和uDS随LS变化的波形(LD与LS和不变) Figure 10 Switching waveforms of uGS, iD and uDS under different LS (under constant sum of LD and LS) |

|

图 11 开关速度随LS变化的曲线(LD与LS和不变) Figure 11 Relationship curves of switching speed under different LS (under constant sum of LD and LS) |

|

图 12 开关能量随LS变化图(LD与LS和不变) Figure 12 Comparisons of switching energy under different LS (under constant sum of LD and LS) |

在关断过程中,LD与LS的总和基本不变的情况下,随着LS的增大,uGS的下降速度也降低,因此漏极电流iD的下降速度和漏极电压uDS的上升速度减慢,关断速度减慢,如图 11(b)所示。关断能量随LS的增大而增大,关断瞬态电压尖峰和开通电流尖峰随LS的增大而减小,如图 13所示。

|

图 13 关断电压与开通电流尖峰随LS变化的曲线(LD与LS和不变) Figure 13 Relationship curves of voltage and current overshoot under different LS (under constant sum of LD and LS) |

由以上实验结果分析可知,在布局受实际因素制约的情况下,若LD与LS总和已很难再进一步减小,则应合理调配LD与LS的大小,满足实际电路要求,其基本规律为:(1) 若增大LS的同时减小LD,这两种寄生电感的变化叠加,使得关断电压尖峰和开通电流尖峰显著减小,满足开关管应力最小的优化目标,但是由于LS对栅极回路的“负反馈”效应,使得开关时间变长,导致开关损耗显著增加;(2) 若在减小LS的同时增大LD,两种寄生电感的变化叠加可使得开关能量显著减小,但是会以增大关断电压尖峰和开通电流尖峰为代价,开关管的电压电流应力增大。所以,在PCB布局受到实际物理限制时,需要根据设计目标优化考虑,若以降低开关管的电压和电流应力为最优目的,可适当增大LS、减小LD;若以低开关损耗为最优设计目标,则应适当减小LS、增大LD。这与之前的理论分析一致。

4 结论本文系统研究了SiC MOSFET各部分寄生电感对器件开关过程的影响,得出了各寄生电感对开关特性的影响规律:

(1) 合理驱动电路的设计一般均要保证栅极回路寄生电感很小,因此寄生电感LG对功率器件开关特性的影响相对较小;

(2) 漏极寄生电感LD对波形振荡和电压尖峰的影响较大;

(3) 源极寄生电感LS对波形振荡和电压尖峰有一定抑制作用,但会使得开关能量损耗增加。

在满足栅极驱动回路与功率回路寄生电感较小,并在布局紧凑程度相对不变的情况下,提出不同优化目标下寄生电感值匹配选择的优化布局方法,通过LS与LD寄生电感值的匹配设计,使得开关电路在物理布局受限的情况下满足不同的开关特性优化目标,从而指导SiC功率器件高速开关电路的优化布局设计。

| [1] |

钱照明, 张军明, 谢小高, 等.

电力电子系统集成研究进展与现状[J]. 电工技术学报, 2006, 21(3): 2–14.

QIAN Zhaoming, ZHANG Junming, XIE Xiaogao, et al. Progress in power electronics system integration[J]. Transactions of China Electrotechnical Society, 2006, 21(3): 2–14. |

| [2] |

王建华, 张国钢, 耿英三, 等.

智能电器最新技术研究及应用发展前景[J]. 电工技术学报, 2015, 30(9): 1–11.

WANG Jianhua, ZHANG Guogang, GENG Yingsan, et al. The latest technology research and application prospects of the intelligent electrical apparatus[J]. Transactions of China Electrotechnical Society, 2015, 30(9): 1–11. |

| [3] |

梁美, 郑琼林, 可翀, 等.

SiC MOSFET?Si CoolMOS和IGBT的特性对比及其在DAB变换器中的应用[J]. 电工技术学报, 2015, 30(12): 41–50.

DOI:10.3969/j.issn.1000-6753.2015.12.006 LIANG Mei, ZHENG Qionglin, KE Chong, et al. Performance comparison of SiC MOSFET, Si CoolMOS, and IGBT for DAB converter[J]. Transactions of China Electrotechnical Society, 2015, 30(12): 41–50. DOI:10.3969/j.issn.1000-6753.2015.12.006 |

| [4] |

严仰光, 秦海鸿, 龚春英, 等.

多电飞机与电力电子[J]. 南京航空航天大学学报, 2014, 46(1): 11–18.

YAN Yangguang, QIN Haihong, GONG Chunying, et al. More electric aircraft and power electronics[J]. Journal of Nanjing University of Aeronautics & Astronautics, 2014, 46(1): 11–18. |

| [5] |

王莉, 朱萍.

新型宽带SiC功率器件在电力电子中的应用[J]. 南京航空航天大学学报, 2014, 46(4): 524–532.

WANG Li, ZHU Ping. Overview of application of SiC power devices in power electronics[J]. Journal of Nanjing University of Aeronautics & Astronautics, 2014, 46(4): 524–532. |

| [6] | Infineon Semiconductor Group. The influence of parasitic network parameters on the switching behavior of power MOSFETs when switching ohmic/inductive loads[EB/OL]. http://www.infineon.com, 2014. |

| [7] | CLEMENTE S, PELLY B R, ISIDORI A. Understanding HEXFET switching performance[EB/OL]. Application Note-947, http://www.irf.com, 2004. |

| [8] | NAYAK P, KRISHNA M V, VASUDEVAKRISHNA K, et al. Study of the effects of parasitic inductances and device capacitances on 1 200 V, 35 A SiC MOSFET based voltage source inverter design[C]// International Conference on Power Electronics, Drives and Energy Systems. Mumbai:[s.n.], 2014: 1-6. |

| [9] | Infineon Semiconductor Group. Advanced power semiconductor devices challenges and solutions in applications[EB/OL]. SiC MOSFET Application Notes, http://www.infineon.com, 2015. |

| [10] | WANG Zhaohui, ZHANG Junming, WU Xinke, et al. Analysis of stray inductance′s influence on SiC MOSFET switching performance[C]//Energy Conversion Congress and Exposition. Pittsburg:[s.n.], 2014: 2838-2843. |

| [11] | CHEN Zheng, BOROYEVICH D, BURGOS R. Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics[C]//Power Electronics Conference. Sapporo:[s.n.], 2010: 164-169. |

| [12] | ANTHON A, HERNANDEZ J C, ZHANG Zhe, et al. Switching investigations on a SiC MOSFET in a TO-247 package[C]//Industrial Electronics Society. Dallas:[s.n.], 2014: 1854-1860. |

| [13] | COUGO B, SCHNEIDER H, MEYNARD T. High current ripple for power density and efficiency improvement in wide bandgap transistor-based buck converters[J]. IEEE Transactions on Power Electronics, 2015, 30(8): 4489–4504. DOI:10.1109/TPEL.2014.2360547 |

| [14] | WANG Jianjing, CHUNG H S H, Li R T H. Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance[J]. IEEE Transactions on Power Electronics, 2013, 28(1): 573–590. DOI:10.1109/TPEL.2012.2195332 |

| [15] | DONG Zezheng, WU Xinke, SHENG Kuang, et al. Impact of common source inductance on switching loss of SiC MOSFET[C]//Future Energy Electronics Conference. Taipei, China:[s.n.], 2015: 1-5. |

| [16] | LI Helong, MUNK-NIELSEN S. Detail study of SiC MOSFET switching characteristics[C]//International Symposium on Power Electronics for Distributed Generation Systems. Rogers:[s.n.], 2014: 1-5. |

| [17] | NOPPAKUNKAJORN J, HAN Di, SARLIOGLU B. Analysis of high-speed PCB with SiC devices by investigating turn-off overvoltage and interconnection inductance influence[J]. IEEE Transactions on Transportation Electrification, 2015, 1(2): 118–125. DOI:10.1109/TTE.2015.2426503 |

2017, Vol. 49

2017, Vol. 49