## 星载高速自适应 SERDES 传输系统设计

刘 吉 许鹏飞 孙垂强 李雄飞

(中国空间技术研究院西安分院,西安,710000)

摘要:针对目前星载处理类载荷数据处理量急剧增加的特点,提出了一种基于 SERDES 技术实现高速数据传输的方法。该方法通过对 SERDES 串行/解串原理的研究,采用了一种自适应调整 SERDES 输入参数的方法,解决了星载处理器要求的不同温度下 FPGA 芯片间高速串行数据传输固有的相位偏移的问题。实验结果表明,该方法实现了在 $-25\sim+60$   $^{\circ}$   $^{\circ}$  温度范围内 78 个通路,333 Mb/s 速率的可靠数据传输,满足了项目的需求,在星上有效载荷芯片间高速数据传输中具有广阔的应用前景。

关键词:星载处理类载荷;高速 SERDES 传输;相位偏移;自适应参数调整

中图分类号:TN927

文献标志码:A

文章编号:1005-2615(2018)S1-0028-05

# Design of High-Speed Adaptive SERDES Technology for Satellite Borne Processor

LIU Ji, XU Pengfei, SUN Chuiqiang, LI Xiongfei (China Academy of Space Technology(Xi'an),Xi'an,710000,China)

**Abstract**: According to the characteristics of the rapid increase in the data processing for the satellite borne processor, a new method based on SERDES technology for high-speed transmission is proposed. Based on the principle of SERDES Serializer/Deserializer, the method adaptively adjusts the SERDES input parameter, and solves the problem of phase shift inherent in high-speed serial data transmission between FPGAs at different temperatures. Experimental result shows that the method can achieve the reliable data transmission of 333 Mb/s of 78 channels at the temperature range of -25 °C to +60 °C, which meets project requirement and is transplantable. The research in the paper provides a wide application prospect in satellite high-speed data transmission.

**Key words:** satellite borne processor; high-speed SERDES transmission; phase shift; adaptive parameter-adjustment

随着中国空间技术的快速发展和用户需求的增加,卫星数字处理载荷的功能和要求日趋复杂,数字处理数据量急剧增加,这对数据传输技术提出了很高的要求[1-2]。

目前卫星数字处理载荷大多使用现场可编程 门阵列(Field programmable gate array,FPGA)芯 片完成数字处理的功能,受宇航级器件性能的限 制,复杂的数字处理功能需要多个芯片进行协作完 成<sup>[3]</sup>,这就需要芯片间完成大量的高速数据传输。 传统的方式是采用并行数据传输,这需要大量占用 芯片有限的 IO 资源,严重制约了系统性能的提升<sup>[4]</sup>。

过去主要用于光纤通信的串行通信技术 SERDES(Serializer/Deserializer,串化/解串器)正 在取代传统的并行总线技术成为高速接口设计 的主流<sup>[5]</sup>,SERDES技术是一种时分多路复用,点 对点的通信技术<sup>[6]</sup>,在发送端将输入的并行数据 转换为串行数据,再经传输线传递到接收端,在 接收端再将串行信号转换成并行信号,这样可以 减少传输线的数目,降低系统成本。同时作为现

收稿日期:2018-03-23;修订日期:2018-05-30

通信作者:刘吉,男,工程师,E-mail:lj\_8821@163.com。

引用格式:刘吉,许鹏飞,孙垂强,等. 星载高速自适应 SERDES 传输系统设计[J]. 南京航空航天大学学报,2018,50 (S1):28-32. LIU Ji,XU Pengfei,SUN Chuiqiang, et al. Design of high-speed adaptive SERDES technology for satellite borne processor[J]. Journal of Nanjing University of Aeronautics & Astronautics,2018,50(S1):28-32.

在多数高端 FPGA 上的一个特殊接口资源, SER-DES 技术成为解决星载高速数据传输的一种很好的方案<sup>[7-9]</sup>。

由于卫星载荷工作环境的特殊性<sup>[10]</sup>,通常要求星载设备在一25~+60 ℃能够正常工作,不同的温度工况给 FPGA 芯片间 SERDES 高速数据传输带来了较大的相位偏移,传统的固定时延的 SERDES 方案已经无法适应星载设备高速传输的要求,本文提出一种利用自适应调整 SERDES 输入参数的方法,解决不同温度下 FPGA 芯片间 SERDES 技术传输固有的相位偏移问题。该方案已经在某卫星通信载荷上得到了成功应用。

#### 1 SERDES 原语

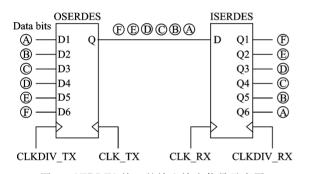

以 Xilinx FPGA 的 SERDES 原语为例,分为 OSERDES 和 ISERDES[11], SERDES 接口的输入输出信号传输流程如图 1 所示。

图 1 SERDES 接口的输入输出信号示意图 Fig. 1 Input and output signal of SERDES interface

OSERDES 原语实现了采样时钟为 CLKDIV\_TX 的低速并行数据转为采样时钟为 CLK\_TX 的高速串行数据,ISERDES 原语实现了采样时钟为 CLK\_DIV\_RX 的高速串行数据转为采样时钟为 CLK-DIV\_RX 的低速并行数据。需要注意的是,并转串直接用 OSERDES 原语实现低速并行数据到高速串行输出的转换,不需要设置相应的参数;而串转并使用 ISERDES 原语在接收高速串行数据时需要确定合适的采样时钟位置和输出并行数据的比特顺序才能保证数据的正确接收,采样时钟位置由参数 IOBDELAY\_VALUE(后文简称 VALUE)进行调整,输出比特顺序由参数 BITSLIP 进行调整 [12]。

## 2 系统总体结构

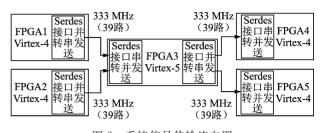

图 2 给出了使用 SERDES 接口的系统硬件 组成,系统的 FPGA 芯片选用 Xilinx 公司的 Virtex-4 系列和 Virtex-5 系列,利用 FPGA 的 SER-DES 接口实现了 78 路信号在 FPGA 之间进行数 据传输,串行速率为 333 Mb/s,并行传输速率为 83.25 Mb/s,其中各 FPGA 之间传输 39 路信号,均为 4 bit 与 1 bit 进行并/串、串/并转换,39 路信号中具体为 1 路 4 bit 训练序列信号,38 路数据信号。

图 2 系统信号传输流向图

Fig. 2 Transmission flow of system signal

并转串发送模块使用 OSERDES 原语,实现 83. 25 Mb/s 的 4 bit 并行数据转为 333 Mb/s 的串行数据进行发送,串转并接收模块使用 ISERDES 原语,实现 333 Mb/s 的串行数据转为 4 bit 的 83. 25 Mb/s的并行数据进行接收。

硬件设计中,各 FPGA 之间的传输数据线采用等长设计,接收模块使用已知的训练序列进行训练,得出 ISERDES 原语需要的时钟偏移量 VAL-UE 值,并行比特顺序调整量 BITSLIP 值,其他数据传输线使用训练出的参数配置 SERDES 原语进行数据的正常接收。

### 3 自适应 SERDES 传输算法设计

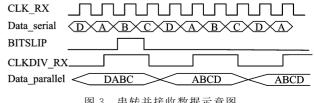

串转并接收模块需要从高速串行数据中正确 采样得到稳态的数据信息,再调整合适的并行数据 比特顺序达到正确接收的目的(图 3)。其中,高速 时钟与数据的采样位置通过 ISERDES 的输入参 数 VALUE 值来调整,并行数据的比特顺序通过 ISERDES 的输入参数 BITSLIP 值来调整,一个 BITSLIP 脉冲使并行数据比特顺序改变一次,对 于 1 转 4 的 ISERDES 原语,BITSLIP 脉冲的数量 有 4 种状态。传统的方法采用固定的 VALUE 值 与 BITSLIP 值来进行正确接收,但固定参数的方 法无法适应高低温变化带来的时钟相位偏移。本 文提出了一种自适应参数变化的接收方法,通过发 送已知的训练序列计算得到实时的输入参数。

图 3 串转并接收数据示意图

Fig. 3 Receiving data with serial to parallel

(1)

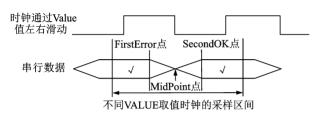

从图 4 可以看出,SERDES 串行传输通过调整 VALUE 值使时钟左右滑动以获得最佳的数据采样位置,VALUE 取值的范围为 0~63,每个VALUE 值的调整步进量由 SERDES 原语的参考时钟决定,ISERDES 原语要求的参考时钟范围为 200±25 MHz<sup>[11]</sup>。以本系统为例,高速串行接收时钟 CLK\_RX 为 333 MHz,参考时钟为 200 MHz,每一个 VALUE 值可调整的时钟偏移量为 78 ps,通过 VALUE 值最大可调整的时钟与数据的位置变化范围约为 5 ns,可以调整大约 1.7倍的串行数据周期,图 4 中对号的区域为正确传输的 VAULE 取值范围,在时钟滑动调整中,记第一个传输错误的 VALUE 点为 FirstError 点,第二次正确传输的点为 SecondOK 点。

图 4 VALUE 值与时钟采样的关系

Fig. 4 Relationship between VALUE and clock sampling

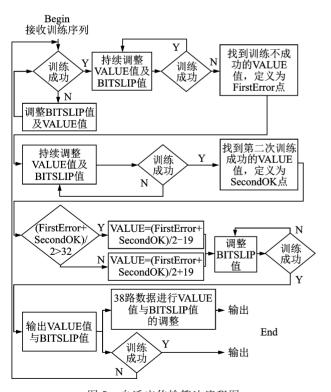

图 5 给出了自适应调整 VALUE 值与 BITS-LIP 调整量的算法流程图,具体的算法描述如下:

图 5 自适应传输算法流程图

Fig. 5 Flow diagram of adaptive transmission algorithm

步骤 1 接收训练序列,训练成功进行步骤 2, 否则持续调整 VALUE 值及 BITSLIP 调整量; 步骤 2 持续调整 VALUE 值及 BITSLIP 调整量直到训练失败,记当前 VALUE 值为 FirstError,转步骤 3;

步骤 3 持续调整 VALUE 值及 BITSLIP 调整量直到训练序列再次成功接收,记当前 VALUE 值为 SecondOK,转步骤 4;

**步骤 4** 进行最终需要的 VALUE 值的计算, 见式(1),转步骤 5;

步骤 5 在当前 VALUE 值下调整 BITSLIP 值直到训练序列正确接收,转步骤 6;

步骤 6 输出当前 VALUE 值与 BITSLIP 调整量,转步骤 7;

步骤 7 32 路数据使用计算得到的 VALUE 值与 BITSLIP 调整量进行数据接收,转步骤 8;

步骤 8 训练序列继续进行实时训练,如正确,训练序列正常输出,否则转步骤 1。

VALUE 值的计算方法为 √VALUE = MidPoint + X, MidPoint ≤ 32;

VALUE = MidPoint - X, MidPoint > 32

记(FirstError+SecondOK)/2=MidPoint,如图 4 所示,即每个数据周期起始的位置。

式(1)中参数 X 的选取由高速串行时钟周期的一半和 SERDES 原语的参考时钟周期决定,X 的调整量为数据周期的一半,本系统 X 取 19,即调整量约为 1.5 ns,数值 32 的选取为 VALUE 最大值的一半。

## 4 软硬件设计

通过大量的实验、调试及理论分析,本方案在软硬件设计时需要考虑以下3点内容,以提高系统工作的稳定性:

- (1) 各 FPGA 之间用于传输训练序列的数据 线与正常数据线需采用等长设计,保证训练序列传 输线的偏移状态与数据传输线的偏移状态一致;

- (2) ISERDES 原语的参考时钟是时钟与数据 采样位置调整的基准时钟,要求时钟频率为 200± 25 MHz,该时钟质量决定了数据传输的稳定性,建 议参考时钟在软件设计中用独立的模块产生或在 硬件设计中直接采用外挂晶振提供时钟的方式;

- (3)对于高速接口设计,FPGA程序资源占用量增大可能导致时钟扇出过大,这样在不同的温度下可能会影响高速接口传输的稳定性,建议在软件设计时将 SERDES 接口需要的时钟与其他处理时钟分开产生。

## 5 实验结果与分析

系统信号传输流向如图 2 所示,其中 FPGA1,

2,4,5 型号为 Virtex-4 系列,FPGA3 型号为 Virtex-5 系列。实验分别对传统固定参数的 SERDES 配置方法和本文提出的自适应参数可变的传输方法在一25,25,60 ℃温度下进行了传输测试,其中 Virtex-4 FPGA 接收处理 39 路信号,Virtex-5 FP-GA 接收处理 78 路信号。

FPGA1,FPGA2 利用 OSERDES 原语各发送 39 路并转串的信号,并行速率为 83. 25 Mb/s,串 行速率为 333 Mb/s,每一路实现 4 bit 转 1 bit 的 传输;FPGA3 利用 ISERDES 原语接收 FPGA1,FPGA2 共 78 路串转并的信号,实现 1 bit 高速串行数据转为 4 bit 低速并行数据的接收,FPGA3 将接收的数据进行交换处理后再利用 OSERDES 原语进行并转串的发送;FPGA4,FPGA5 利用 ISERDES 原语各进行 39 路串转并的数据接收。

实验中 FPGA1, FPGA2 发送已知波形的数据,利用 ISE 的 Chipscope 调试工具观测 78 路数据的接收情况,因为 FPGA4, FPGA5 为最后一级接收,只需要观测这两个芯片的接收正确与否就可以得到整个系统的传输状态。

#### 5.1 传统固定参数的方法

传统方法采用遍历 VALUE 值与 BITSLIP 值 最终固定一个合适的参数进行 ISERDES 原语参数配置,实现串转并信号的正常接收。但在程序进行时序改变时,可能需要重新进行遍历并确定合适的参数。

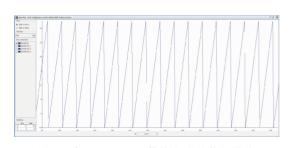

图 6 显示了 FPGA4 中任意一路信号在常温 25 ℃数据的接收情况,通过遍历所得到的 VAL-UE 值和 BITSLIP 调整量可以实现正确传输。

图 6 常温(25 ℃)下传统方法的数据接收

Fig. 6 Receiving data with traditional method at normal temperature(25  $^{\circ}\mathrm{C}$  )

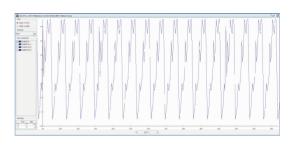

图 7 中采用与图 6 相同的参数,观测同一路信号,可见传输信号已经出现毛刺的现象,表明数据传输过程中出现误码。这是由于温度的变化带来了高速时钟的相位偏移,常温下选用的 VALUE 值无法匹配高温下数据传输。传统选用固定参数的方法无法适应温度变化带来的相位偏移。

#### 5.2 自适应调整 SERDES 输入参数的方法

图 8 显示了 FPGA4 中接收的任意一路的数

图 7 高温(60 ℃)下传统方法的数据接收

Fig. 7 Receiving data with traditional method at high temperature (60  $^{\circ}\mathrm{C}$  )

图 8 低温 $(-25 \, ^{\circ})$ 、常温 $(25 \, ^{\circ})$ 、高温 $(60 \, ^{\circ})$ 下自适应 调整参数方法的数据传输

Fig. 8 Receiving data with adaptive transmission method at different temperature(-25,25,60 °C)

据,在低温 $(-25 \, ^{\circ} \, ^{\circ})$ 、常温 $(25 \, ^{\circ} \, ^{\circ})$ 、高温 $(60 \, ^{\circ} \, ^{\circ})$ 不同温度范围下,通过长时间的观测,数据都可以正确并稳定地接收。本文提出的自适应调整 SERDES 参数的方法解决了 FPGA 芯片间不同温度下带来的时钟相位偏移的问题,通过实时地调整 VALUE 值和 BITSLIP 调整量来保证数据的稳定接收。

#### 6 结束语

对于星载数字处理载荷芯片间数据高速传输的需求,本文利用 FPGA 芯片的 SERDES 接口,通过实时地计算输入参数,提出了一种自适应的高速数据传输的设计方法,解决了 FPGA 芯片间不同温度下多路 SERDES 接口传输固有的相位偏移问题。按照这种方法设计的高速数据传输方案,可以保证星载设备在要求的一25~+60 ℃温度范围内可靠稳定地进行数据传输,文中给出的实验结果说明了该方法的有效性。

#### 参考文献:

[1] 刘振华. 未来通信卫星的发展趋势[J]. 硅谷,2014 (9):3-28,

LIU Zhenhua. The development trend of future communication satellite[J]. Silicon Valley, 2014(9):3-28

[2] 刘乃金,陈东,梁宗闯,等. 移动通信卫星星载数字处

理器件需求分析与方案设计[J]. 航天标准化,2011 (3):13-17.

LIU Naijin, CHEN Dong, LIANG Zongchuang, et al. Demand analysis and scheme design of mobile communication satellite digital processor [J]. Space Standardization, 2011(3):13-17.

- [3] 刘军峰,张彦,马婷. 星载高速 SERDES 电路的设计与实现[J]. 空间电子技术,2014,4(13):55-59. LIU Junfeng, ZHANG Yan, MA Ting. The design and application of high-speed serdes circuit for satellite borne processor[J]. Space Electronic Technology, 2014, 4(13):55-59.

- [4] 李优杏,周先敏,吕红军. 基于 FPGA 的 SERDES 接口设计与实现[C]//中国通信学会第五届学术年会. [S. l.]:CST, 2008.

LI Youxing, ZHOU Xianmin, LV Hongjun. Design and realization of SERDES interface base on FPGA [C]. The 5th Annual Academic Conference of China Communication Association. [S.1]:CST, 2008.

- [5] STAUFFER D R, MECHLER J T, SOMA M A. High-speed serdes devices and applications[M]. [S. l.]:Springer Science & Business Media, 2008.

- [6] LEWIS D. SERDES architectures and applications [C] // Proceedings of Euro Design Con. Chicago, USA: [s. n. ], 2004.

- [7] 王张萌. 高速 SERDES 接口的关键电路设计[D]. 合肥:合肥工业大学,2012.

- WANG Zhangmeng. The key circuits design of hign-speed SERDES interface[D]. Hefei: Hefei University of Technology, 2012.

- [8] 张亚东. 高速 SERDES 接口芯片中抖动仿真技术的研究[D]. 成都:电子科技大学,2013.

ZHANG Yadong. Research on jitter simulation technology applied in high-speed SERDES chip [D].

Chengdu: University of Electronic Science and Technology of China, 2013

- [9] ZHANG W, HU W, DING R. Research on high-speed asynchronous serial transmission based on 8b10b[M]. [S. l.]; Spring Berlin Heidelberg, 2011.

- [10] 胡明亮. 卫星单机的热分析仿真与测温研究[D]. 上海: 上海交通大学, 2008.

HU Mingliang. Research about the thermal simulation and infrared temperature measurement of satellite instruments [D]. Shanghai: Shanghai Jiaotong University, 2008.

- [11] XI LINX CORPORATION. Virtex-4 FPGA user guide[R]. [S. l.]: Xilinx Inc, 2008.

- [12] 刘丽格,李天保,石鑫刚. 一种板间高速传输系统的设计与实现[J]. 工程实践与应用技术,2011,37(4):53-55.

- LIU Lige, LI Tianbao, SHI Xingang. Design and implementation of a high-speed board-to-board transmission system[J]. Engineering Practice and Application Technology, 2011,37(4):53-55.

(编辑:夏道家)